Softwarové ovladače pro automobilový pohon v procesoru pro AURIX 2G

Tento software tvoří kostru pro začlenění regulačních algoritmů schopných pracovat při funkční poruše a diagnostických algoritmů vícefázových motorů vygenerovaných z nástrojů MATLAB/Simulink na platformě šesti-jádrového mikrokontroléru AURIX 2G určeného pro aplikace s vysokou mírou bezpečnosti. Je tím umožněno testování řízení pohonů při poruše v reálné aplikaci s reálným motorem a měničem. Hlavní částí SW jsou strukturované ovladače periferií mikrokontroléru AURIX 2G založené na iLLD (PWM modulátor, SAR a DS AD převodníky, GPIO) pro dva subsystémy vícefázového motoru (dvakrát třífázový motor).

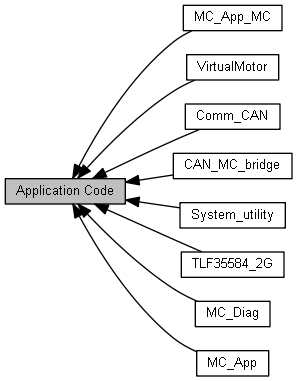

Obrázek 1: Struktura vytvořených ovladačů

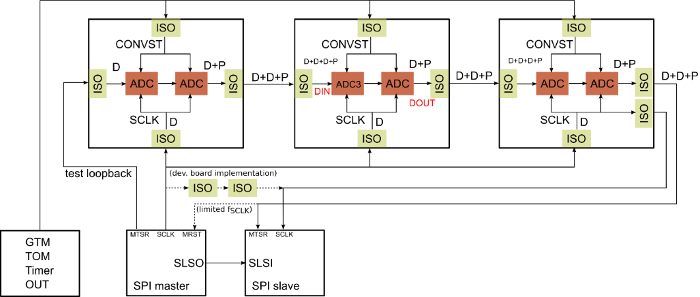

Staticky definované konfigurace periferií umožňující adaptaci finálního HW konkrétního výkonového měniče. Uvažuje se použití rychlých komunikačních sběrnic obvodů snímání regulovaných veličin s vysokým rozlišením (SPI sensory proudu, I2C měření napětí a teploty).

Obrázek 2: Vytvořené schéma izolovaného SPI zapojení pro sběr naměřených dat

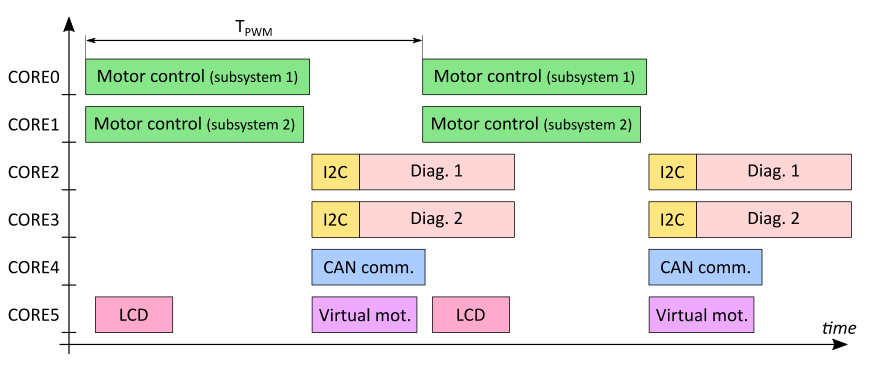

Součástí návrhu SW ovladačů periferií mikrokontroléru je také návrh mapy připojení pinů mikrokontroléru k jednotlivým subsystémům měniče s ohledem na potlačení vlivu společné chyby HW (common-cause failure). Pro komunikaci s nadřazeným systémem je implementována komunikační sběrnice CAN, která je definována pomocí DBC souborů. Ovladače jednotlivých periferií použitých pro řízení motoru umožňují aktivaci testovacího režimu. V tomto testovacím režimu jsou fyzické signály nahrazeny signály virtuálního motoru, který je implementovaný v SW a je spouštěn na jednom z volných jader mikrokontroléru. Virtuální motor umožňuje testování celé regulačních smyčky motoru v reálném čase ještě před použitím algoritmů na reálném výkonovém měniči.

Obrázek 3: Rozdělení algoritmů v jádrech procesoru AURIX

Technické parametry

- Určeno k testování algoritmů řízení vícefázových PMSM vytvořených v MATLAB/Simulink s vygenerovaným C kódem.

- Připraveno pro redundantní architekturu dvou subsystémů (2x3 fázový měnič a motor) pro zvýšení spolehlivosti.

- Strukturované ovladače periferií mikrokontroléru AURIX 2G se statickou definicí konfigurace subsystémů.

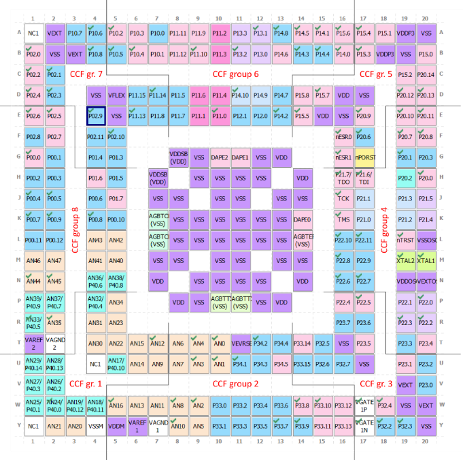

- Návrh rozložení pinů mikrokontroléru subsystémům s ohledem na společné chyby HW.

- CAN komunikace s nadřazeným systémem pomocí CAN sběrnice definované DBC soubory.

Obrázek 4: Rozložení pinů mikrokontroléru s ohledem na souhlasné chyby HW